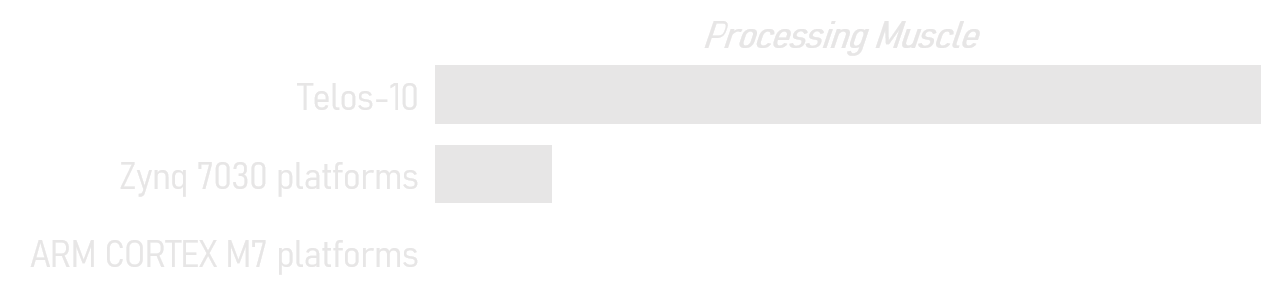

To overcome hurdles associated with our own pursuits, we developed the most powerful compute platform, for both single- and double-precision operations, compatible with nanosatellites. The entry-level Telos OBC is 7x more powerful than the current state-of-the-art. It utilises bleeding-edge FPGA technologies otherwise unavailable to the sector. If you need some serious processing-punch, this is the best you’re going to find.

Telos is a one-step solution for a variety of advanced compute applications such as:

Signal/image processing systems

AI & Machine Learning

Constellation Management

-

- Reliability, fault tolerance and SEU protection are improved though TMR and EDAC on data and logic

- Supplied with OrbAstro flight software or a Linux platform to accelerate applications development (no embedded systems or space electronics expertise required)

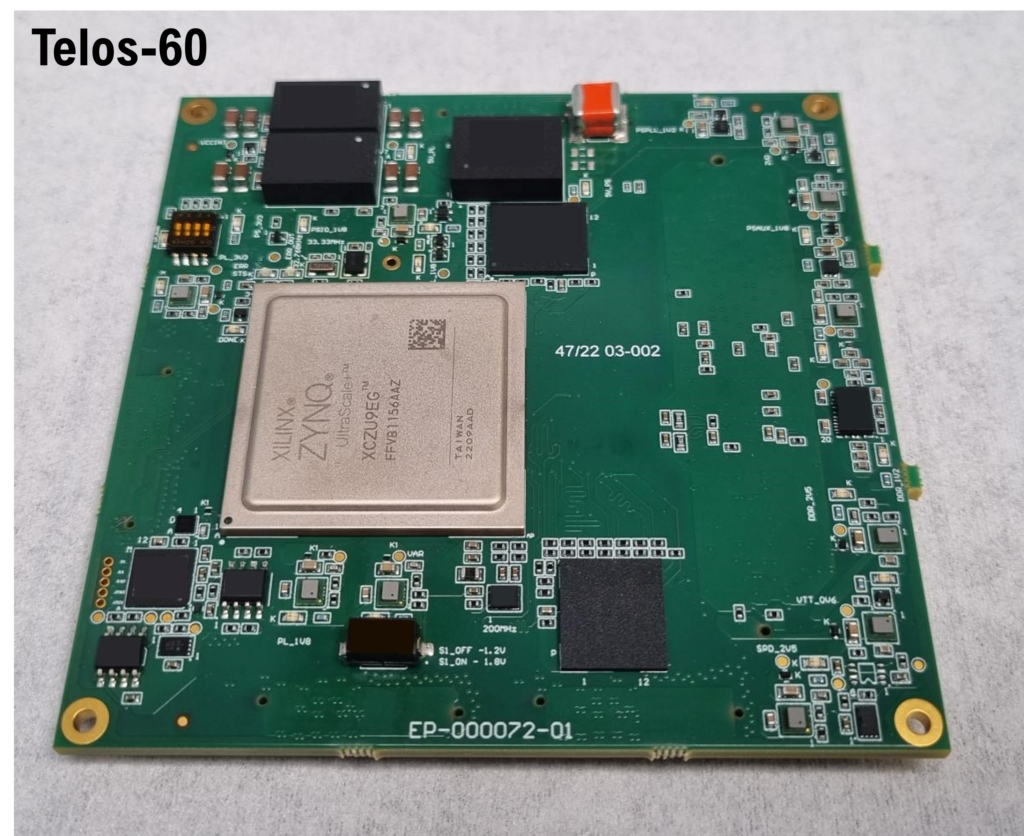

- Based on Xilinx Ultrascale+ MPSoCs with ARM cortex A53 and R5 64-bit processing cores, combined with LPDDR4 memory

- Optional extras include the addition of Kintex and Virtex based FPGAs.

- Mechanical and electrical interfaces are customisable with external docks; compatible with PC-104 CubeSat standard

- Supports CV and ANN

- Flight heritage of Telos 10 and Telos 40 series in June-21 and again in Dec-21.

|

Spec |

Telos 10 series |

Telos 40 series |

Telos 60 series |

|

Price (starting from) |

£5,000 |

£8,000 |

£32,000 |

|

A53 |

Dual core @ 1.3GHz |

Quad core @ 1.5GHz |

Quad core @ 1.5GHz |

|

R5 |

Dual core @ 0.5GHz |

Dual core @ 0.6GHz |

Dual core @ 0.6GHz |

|

FPGA |

0.24k – 3.1k DSP blocks, 103k – 730k Logic cells |

0.24k – 3.1k DSP blocks, 103k – 730k Logic cells |

1.9k – 21.3k DSP blocks, 469k – 6451k Logic cells |

|

DRAM |

Up to 4GB (EDAC) |

Up to 16GB (EDAC) |

Up to 64GB (EDAC) |

|

Peak Performance |

1 TFLOPs |

1 – 5 TFLOPs |

3 – 15 TFLOPs |

|

Max DRAM data rate |

>9GB/s |

>9GB/s |

>>200GB/s |

|

Max. Flash |

128GB (EDAC) |

256GB (EDAC) |

1TB (EDAC) |

|

General Interfaces |

4xI2C Master/slave, 4xSPI Master/slave, 4xRS422/RS485, 2x CAN, 1x USB 2.0, Ethernet 10/100/1000Mbps |

4xI2C Master/slave, 4xSPI Master/slave, 4xRS422/RS485, 2x CAN, 1x USB 2.0, Ethernet 10/100/1000Mbps |

4xI2C Master/slave, 4xSPI Master/slave, 4xRS422/RS485, 2x CAN, 1x USB 2.0, Ethernet 10/100/1000Mbps |

|

High Speed Interfaces |

Up to 40x LVDS @ 1.2Gbps, 4x PCIe G2 |

Up to 40x LVDS @ 1.2Gbps, 4x PCIe G2, 1x 10G Ethernet |

40x LVDS @ 1.2Gbps, 4x PCIe G3, 40x Gigabit Transceivers @ 32Gbps, 1x 10G Ethernet |

|

Radiation Tolerance* |

>400krad (TiD), SEU protection on DRAM and Flash |

>400krad (TiD), SEU protection on DRAM and Flash |

>400krad (TiD), SEU protection on DRAM and Flash |

|

Operating Temp. Range |

-20°C to +60°C |

-20°C to +60°C |

-20°C to +60°C |

|

Survival Temp. Range |

-30°C to +100°C |

-30°C to +100°C |

-30°C to +100°C |

|

Operating Voltage |

5 – 60V |

5 – 60V |

5 – 60V |

|

Power Consumption |

0.5 – 8W |

0.5 – 12W |

0.5 – 40W |

|

Mass |

30g (120g with heat sink) |

30g (120g with heat sink) |

90g (195g with heat sink) |

|

Dimensions |

48x48x7mm (without redundancy) |

48x48x7mm (without redundancy) |

95x95x10mm (without redundancy) |

|

Redundancy |

Dual Redundant (optional) |

Dual Redundant (optional) |

Dual Redundant (optional) |

*Radiation testing conducted with a 60MeV proton source

|

Spec |

OrbAstro Telos 10 series |

Zynq 7030 Architecture |

ARM Cortex M7 Architecture |

|

Speed |

750x |

125x |

1x (baseline) |

|

Benchmark Algorithm Time (μs)* |

0.176 |

1.053 |

131.425 |

|

Max Power Consumption |

8W |

5W |

1.5W |

|

Low Power Mode** |

0.26W |

1.1W |

1.5W |

|

RAM |

LPDDR4 (4GB baseline, up to 32GB on request) |

DDR3 (1GB) |

DRAM (2MB) |

|

Size |

48x45x7mm |

65x40x7mm |

95x95x12mm |

|

Mass |

30g |

77g |

60g |

*Measured compute time for each system to process a complex orbital dynamics algorithm

**Performance per specific energy

Get in touch: hello@orbastro.com